# The Fir Filter Design and Analysis and Code Generation Using HDLCODER for Area and Power Efficient FPGA Implementation

Mayuri P.Chaudhari M.Tech PCE,Nagpur, India.

Dr.S.S.Shriramwar H.O.D Electronics Eng.PCE,Nagpur, India.

Abstract – Nowdays the digital signal processing is highly demanded as the competition amongst the different electronics companies is increasing to fulfill the demands of the consumers and hence the equalisers, filters need to be modified according to the requirements. Before dealing with the design of the filter we must analyse the filters this paper shows the analysis reports of different filters using FIR design in Filter design and Analysis tool (FDA) .DSP operation mainly include the Multiply and Accumulate MAC operation so we have designed RAM based FIR filter using HDLcoder in simulink where MAC is taken into the consideration. Also the Code generated by the HDL coder is implemented on the Xilinx ISE 14.7 .ISim vhdl simulator is used for simulation. The model is synthesized. RTL and Technology schematic is observed.

## Index Terms – MATLAB,fdatool,HDLcoderFPGA,FIR

# 1. INTRODUCTION

The filter designing has become basic requirement of any communication system or software radio or even the image and video-audio processing to achieve lossless systems. However, when dealing with the IIR filter or recursive filters we have to deal with the extreme unstable impulse response though its accuracy is high. The filter is implemented on SPARTAN 6 low power device.

## 2. PROPOSED WORK

As In signal processing, a finite impulse response (FIR) filter is a filter whose impulse response (or response to any finite length input) is of finite duration, because it settles to zero in finite time. The impulse response of an Nth- order discrete-time FIR filter lasts for N + 1 samples, and then settles to zero[1]. A Finite impulse response (FIR) filter is a filter structure that can be used to implement almost any sort of frequency response digitally. An FIR filter is usually implemented by using a series of delays, multipliers and adders to create the filter output. Figure 1 shows the basic block diagram for an FIR filter of length N. The delays in operating on prior input samples. The hk values are the coefficients used for multiplication, so that the output at time n is the summation of all the delayed samples multiplied by the appropriate coefficients. The processer selecting the filters length and coefficients is called as filter design. Dealing with MATLAB environment we have to consider some presumptions like to know about different tools integrated in it. As the FDAtool is used to analyse the implementation.No explicit multipliers are used in the design, this includes look-up tables (LUTs), shift registers, and a scaling accumulator for the computations.

## 3. SOFTWARE USED

To generate the filter code we used FDA tool HDLcoderof MATLAB And Xilinx ISE.14.7(64-bit)Xilinx Designing a digital filter in MATLAB and using HDL coder FIR filter code is generated and programming it onto an

FPGA.MATLAB

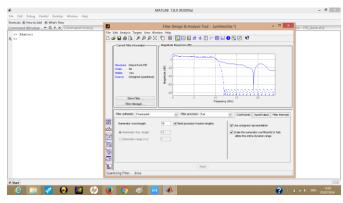

## fdatool is as shown in figure 1

Figure 1: MATLAB fdatool window

## 4. FLOW OF WORK

The filter coefficients obtained by quantising the filter using a "set quantization parameters" at the bottom left of the fdatool window. As we want RAM to be used in the FPGA implementation we must specify the quantization parameters as double precision floating point as the FPGA supports only floating point coefficients it is convinient to use the fdatool.

Figure 2: The quanitization Parameters

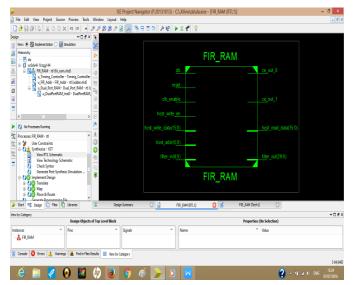

The RTL logic of The RAM based FIR is as shown in the figure below

Figure 3: The top level entity

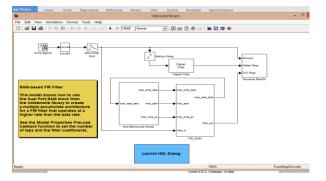

The RAM based Structure of FIR filter is designed using HDLcoder by giving a command "hdlcoderfirram.mdli" in

MATLAB command window we get the RAM based FIR filter and its associate blocks as shown in the figure 4.

Figure 4.HDL coder dialog

After pressing the "LAUNCH HDL DIALOGUE" we get the following window in figure 5 where choose the code generation output as generate code and display generated model. Press "Generate" button to get the display as shown in figure 5

| Data Import/Export                                | File name: noicoo                   | ernram_control                   |   | LOBG                      |

|---------------------------------------------------|-------------------------------------|----------------------------------|---|---------------------------|

| Optimization<br>Diagnostics                       |                                     |                                  |   | Save                      |

| Sample Time<br>Data Validity                      | Target                              |                                  |   |                           |

| Type Conversion<br>Connectivity                   | Generate HDL for:                   | hdlcoderfirram/FIR_RAM           | • |                           |

| Compatibility                                     | Language:                           | VHDL                             | - |                           |

| -Model Referencing<br>Saving                      | Directory:                          | hdisrc                           |   | Browse                    |

| ardware Implementation<br>odel Referencing        | Code generation or                  | utput                            |   |                           |

| nulation Target<br>Symbols                        | O Generate HDL                      |                                  |   |                           |

| -Custom Code                                      | <ul> <li>Display general</li> </ul> | ted model only                   |   |                           |

| al-Time Workshop<br>Report                        | Generate HDL                        | code and display generated model |   |                           |

| Comments<br>Symbols                               | Generate tracea                     | bility report                    |   | Run Compatibility Checker |

| Custom Code<br>Debug<br>Interface                 | Restore Factory                     | Defaults                         |   | Generate                  |

| L Coder                                           |                                     |                                  |   |                           |

| Global Settings<br>Test Bench<br>EDA Tool Scripts |                                     |                                  |   |                           |

Figure 5: Configuration parameters

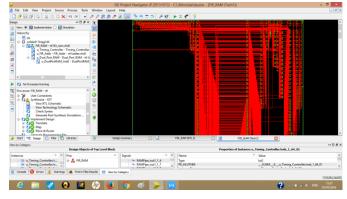

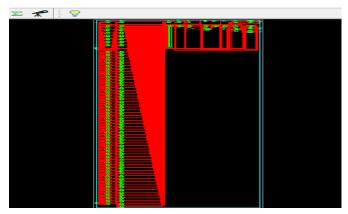

Figure 6:Technology schematic of Dual port RAM based FIR filter

The technology schematic is as shown in figurw It consists of LUTs describing Accumulator,FIR\_RAM,Tapped delay.The design properties are shown in the figure the simulation tool is ISim and Package is TQG144 also the speed grade is -1L and the device it can be implemented on is XC6SLX4L.The Xilinx ISE environment is used to synthesize the code and implement the design.The device utilization summery i as shown in the table.

| Slice Logic Utilization            | Used | Available | Utilization |

|------------------------------------|------|-----------|-------------|

| Number of Slice Registers          | 798  | 4,800     | 16%         |

| Number of Slice LUTs               | 491  | 2,400     | 2.0%        |

| Number used as logic               | 300  | 2,400     | 1.2%        |

| Number used as Memory              | 32   | 1,200     | 2%          |

| Number of occupied Slices          | 215  | 600       | 3.5%        |

| Number of MUX CYs use d            | 32   | 1,200     | 2%          |

| Number of LUT Flip Flop pairs used | 7 36 |           |             |

| Number of bonded <u>IOBs</u>       | 84   | 102       | 8 2%        |

| Number of BUFG/BUFGMUXs            | 1    | 16        | 6%          |

| Number of DSP48A1s                 | 1    | 8         | 12%         |

| Average Fanout of Non-Clock Nets   | 3.64 |           |             |

# International Journal of Emerging Technologies in Engineering Research (IJETER) Volume 4, Issue 7, July (2016) www.ijeter.everscience.org

| •                                      | Des                                                 | ign Properties       |              | - |  |  |

|----------------------------------------|-----------------------------------------------------|----------------------|--------------|---|--|--|

| Name:                                  | da                                                  | da                   |              |   |  |  |

| ocation:                               | C:\.Xilinx                                          | C:\.Xilinx\da        |              |   |  |  |

| Norking directory:                     | C:\.Xilinx                                          | C:\.Xilinx\da        |              |   |  |  |

| Description:                           | MATLAB generated code for RAM based FIR filter(MAC) |                      |              |   |  |  |

| Project Settings                       |                                                     |                      |              |   |  |  |

|                                        |                                                     |                      |              | ^ |  |  |

| Evaluation Development B               | Board                                               | None Specified       | $\checkmark$ |   |  |  |

| Product Category                       |                                                     | All                  | ~            |   |  |  |

| Family                                 |                                                     | Spartan6 Lower Power | $\mathbf{v}$ |   |  |  |

| Device                                 |                                                     | XC6SLX4L             | ~            |   |  |  |

| Package                                |                                                     | TQG144               | $\mathbf{v}$ |   |  |  |

| Speed                                  |                                                     | -1L                  | ~            |   |  |  |

|                                        |                                                     |                      |              |   |  |  |

| Synthesis Tool                         |                                                     | XST (VHDL/Verilog)   | ž            |   |  |  |

| Simulator                              |                                                     | ISim (VHDL/Verilog)  |              |   |  |  |

| Preferred Language                     |                                                     | VHDL                 | ~            |   |  |  |

| Property Specification in Project File |                                                     | Store all values     | $\mathbf{v}$ |   |  |  |

| Manual Compile Order                   |                                                     |                      |              |   |  |  |

| VHDL Source Analysis Sta               | ndard                                               |                      |              | ~ |  |  |

|                                        |                                                     | OK Cancel H          | elp          |   |  |  |

|                                        |                                                     |                      |              |   |  |  |

Figure 7: The design properties

The RTL schematic can show that the number of LUTs are more but the FPGA LUTs consumes less power as compared to the other DSP tools.

Figure 8.RTL Schematic of filter

# 5. SYNTHESIS REPORT

1. Advanced HDL Synthesis Report

Macro Statistics

| # RAMs                              | :1  |

|-------------------------------------|-----|

| 64x16-bit dual-port distributed RAM | : 1 |

| # Multipliers                       | : 1 |

| 16x10-bitregistered multiplier      | :1  |

| # Counters                          | : 2 |

| 6-bit up counter                    | : 2 |

| # Accumulators                      | : 1 |

| 30-bit up loadable accumulator | :1     |

|--------------------------------|--------|

| # Registers                    | : 1392 |

| Flip-Flops                     | : 1392 |

| # Multiplexers                 | : 3    |

| 10-bit 64-to-1 multiplexer     | : 1    |

| 16-bit 2-to-1 multiplexer      | : 1    |

| 30-bit 2-to-1 multiplexer      | : 1    |

| D                              |        |

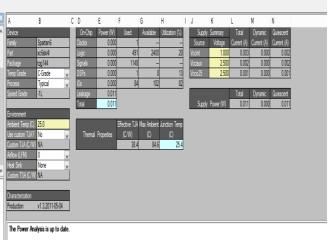

Power report

The .ncd file is shows the power consumed by different part of the system i.e.on chip power,clocks,DSPs,logic,signals,IOs etc.Using a Xilinx Power analyser the power is estimated as shown in figure 9.

(1) Place mouse over the asterisk for more detailed BRAM utilization.

# Figure 9:Xilinx Power Analyser

# 6. FUTURE SCOPE

In the Distributed arithmetic architecture shared-LUT design is proposed to realize DA computation.Dual port distributed RAM based LUTs are being used.DA decomposition for implementation of an FIR filter is the first thing to do.The proposed work also involves clock gating.

# 7. RESULTS AND CONCLUSION

The junction temperature found to be 25.10 C and the leakage power is 0.011W. On-Chip Power Summary is given in the table

| 7.1 On-Chip | Power (mW) | Used | Available | Utilization |

|-------------|------------|------|-----------|-------------|

| (%)         |            |      |           |             |

| Clocks | 0.40 | 1 | ---- | ---- |

| Logic                      |  | 0.00  | 491  | 2400 |  | 20 |

|----------------------------|--|-------|------|------|--|----|

| Signals                    |  | 0.00  | 1148 |      |  |    |

| IOs                        |  | 0.00  | 84   | 102  |  | 82 |

| DSPs                       |  | 0.00  | 1    | 8    |  | 13 |

| Static Power               |  | 10.97 |      |      |  |    |

| Total                      |  | 11.36 |      |      |  |    |

| 7.2. Thermal Summary       |  |       |      |      |  |    |

|                            |  |       |      |      |  |    |

| Effective TJA (C/W)   38.4 |  |       |      |      |  |    |

| Max Ambient (C)   84.6     |  |       |      |      |  |    |

| Junction Temp (C)   25.4   |  |       |      |      |  |    |

-----

7.3. Power Supply Summary

\_\_\_\_\_

|                   | Total | Dynamic   Static Po |       |  |

|-------------------|-------|---------------------|-------|--|

| Supply Power (mW) | 11.36 | 0.40                | 10.97 |  |

The HDL code generated is efficient The study of FIR filter design shows that it is linear phase and stable and therefore can be used in various applications to reduce the noise or can be used for waveshaping.

#### REFERENCES

- Chandak, P.R., Giradkar, V.P & Wadmalwar, A.T., (February 2015) "Design of FIR filter using Matlab Simulink and Xilinx system Generator" International Journal Of Engineering And Computer Science ISSN:2319-7242 Volume 4 Issue 2 Page No. 10384-10387.

- [2] Kamble, P., Deote, N., Wanjari, N., & Prof. Gaikwad, S., (January 2015) "Implementation of FIR Filter Structure for Audio Application Using Xilinx System Generator" International Journal of Advanced Research in Computer Science and Software Engineering Volume 5, Issue 1, ISSN: 2277 128X.

- [3] Dewasthale, M.M. & Dr. Kharadkar ,R.D., (2014) "Improved NLMS Algorithm with Fixed Step Size and Filter Length using Adaptive Weight Updating for Acoustic Noise Cancellation" Annual IEEE India Conference (INDICON)978-1-4799-5364-6/14/.

- [4] Maurya, L., Srivastava, V. K., & Mehra, R., (Feb-2014) "Simulink based design simulations of band pass FIR filter" IJRET: International Journal of Research in Engineering and Technology eISSN: 2319-1163 | pISSN: 2321-7308 Volume: 03 Issue: 02 |[5] Gaikwad, S.R. & Dekate, K.N.,(Oct.-Nov.2014)"Design of FIR Filter for Audio Application" International Journal of Emerging Trends in Engineering and Development Issue 4, Vol.6 ISSN 2249-6149.

- [5] Gaikwad, S.R., & Gawande, G. S., (2014) "Design and Implementation of Efficient FIR Filter Structures using Xilinx System Generator" International Journal of scientific research and management (IJSRM) Volume-2,Issue-3,Pages-599-604.

- [6] Rao, C.M., Dr. Charles, B. S. & Dr. Prasad, M.N.G., (July 2013) "A Variation of LMS Algorithm for Noise Cancellation" International Journal of Advanced Research in Computer and Communication Engineering, Vol. 2, Issue 7, ISSN: 2319-5940.

- [7] Aggarwal, A., Satija A., & Nagpal T., (April 2013) "FIR Filter Designing using Xilinx System Generator", International Journal of Computer Applications (0975 – 8887), Volume 68– No.11,. [9] Patel, S., (October 2013) "Design and Implementation of 31-order FIR Low-pass Filter using Modified Distributed Arithmetic based on FPGA" International Journal of Advanced Research in Electrical, Electronics and Instrumentation Engineering Vol. 2, Issue 10, ISSN: 2320 – 3765.

- [8] Kumar, T. & A.,SMIEEE,(2013) "Low Power VLSI Implementation of Adaptive Noise Canceller Based on Least Mean Square Algorithm" International

- [9] Yadav, J., Kumar, M., Saxena, R. & Jaiswal, A. K., (June 2014) "Performance analysis of LMS adaptive FIR filter and RLS adaptive FIR filter For noise cancellation" Signal & image processing : an international journal (SIPIJ)vol.4, no.3, 4304.

Authors

Mayuri P.Chaudhari has earned B.E. in Electronics and telecommunication from Ram Meghe Institute of Technology and research, Badnera,Amaravti University,Maharashtra,India in 2013 and pursuing M.Tech forth sem in Communication from Priyadarshini college of Engineering, Nagpur,Maharashtra, India. Her area of research is signal processing and FPGA.

**Dr.S.S.Shriramwar** is M.Tech. and Ph.D. in Electronics Engineering having teaching experience of 21 years. He is working as a professor and Head in Electronics Engineering Department, Priyadarshini College of Engineering Nagpur (RTMNU Nagpur University). His research area is FPGA based Designs and Hardware Reconfiguration of FPGA. He has published 31 research papers in International Journals and conferences. He has guided 20 PG Projects and 2 Ph.D. scholars.